SMPS Low-Noise Layout Techniques

🧩 The Problem :

Switch Mode Power Supplies (SMPS) are compact and efficient—but they can be noisy! Poor PCB layout can cause high-frequency switching noise to interfere with sensitive analog or digital circuits, leading to erratic behavior.

🛠️ The Solution :

Good layout minimizes noise. Key rules:

Keep high-current loops (like switch and diode paths) as short and thick as possible.

Place input and output capacitors close to the switching IC.

Use a solid ground plane to reduce EMI.

Separate power and signal grounds with a single point connection.

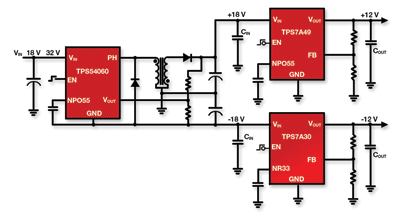

💡 Practical Example :

If you’re building a DIY IoT controller with a buck converter for 3.3V from 12V, placing the input capacitor far from the IC may cause unstable voltage and RF noise. Replacing the layout to shorten the path and adding a ferrite bead fixes it instantly.

🧮 Sample Solution :

Using a 10µF ceramic capacitor (X7R) close to the IC reduces ripple.

Ripple voltage ≈ I / (f × C)

If I = 0.5A, f = 100kHz, C = 10µF:

Ripple ≈ 0.5 / (100,000 × 10e-6) = 0.5V — too high! Add a 100µF electrolytic in parallel to drop ripple further.

🛒 Product Suggestions :

🔗 Flux

🔗 MOSFET

Shop now at SmartXProKits.in

🇮🇳 Support our work and India’s innovation—buy from our Make in India site!